# Лабораторная работа №2. Исследование работы триггеров.

Кафедра ВС СибГУТИ

2012 год

## Содержание

| 1. Цель работы:                         | 3 |

|-----------------------------------------|---|

| 2. Общие сведения                       | 3 |

| 3. Асинхронный RS-триггер               | 4 |

| 4. Синхронный одноступенчатый D-триггер | 6 |

| 5. Задание на лабораторную работу       | 7 |

| 6. Содержание отчёта                    | 8 |

| 7. Контрольные вопросы:                 | 8 |

#### 1. Цель работы:

- 1. Ознакомиться с назначением и принципом действия триггеров.

- 2. Ознакомиться с практическими схемами RS, D триггеров и исследовать их.

#### 2. Общие сведения

Триггер - электронная схема с двумя устойчивыми состояниями. Схема триггера на электронных лампах была предложена в 1918 году русским учёным М.А.Бонч-Бруевичем. Одно состояние триггера принимается за нулевое, другое состояние принимается за единичное.

Термин триггер происходит от английского слова trigger - защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает "хлопанье". Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить ("перебрасываться") из одного электрического состояния в другое и наоборот.

Обычно триггер строится на основе двух инверторов, выход одного из которых считается прямым выходом триггера, а выход другого инвертора считается инверсным. Состояние прямого выхода определяет состояние триггера. Символом триггера на схемах является буква Т.

Поведение триггера описывается матрицей или таблицей переходов. Различают полную и сокращенную таблицу переходов. В полной таблице переходов определяется последующее состояние триггера Q(t+1) в зависимости от состояний входных информационных сигналов и предыдущего состояния триггера:

$$Q(t+1)=f(Q(t),xi(t)).$$

Сокращенная таблица переходов не принимает в расчёт предыдущее состояние триггера, поскольку поведение триггера полностью определяется состоянием входных сигналов. У триггера различают информационные входы и входы синхронизации, помечаемые символом С (от слова Clock). По каждому входу определяют понятие активного сигнала. Активным сигналом может быть уровень (ноль или единица) или фронт сигнала (нарастающий или спадающий). Активный сигнал определяет поведение триггера в следующий момент времени. Если триггер не имеет входов синхронизации, то его называют асинхронным.

В этом случае его поведение однозначно определяется в момент прихода активного сигнала по информационному входу. В зависимости от условного обозначения входа триггер будет изменять своё состояние или под действием уровня входного сигнала или под действием фронта этого сигнала. Информационные входы имеют буквенные идентификаторы, которые соответствуют их назначению.

Если триггер имеет хотя бы один вход синхронизации, то он считается синхронным. У такого триггера имеются информационные входы, приём информации по которым происходит в момент активного синхросигнала. Независимо от этих входов триггер может иметь и другие информационные входы, которые асинхронно или синхронно определяют поведение триггера.

В зависимости от того, какой сигнал является активным по входу синхронизации, различают триггеры потенциальные (со статическим управлением) или управляемые по уровню и триггеры с динамическим управлением или срабатывающие по фронту.

В некоторых триггерах под действием определённой комбинации информационных сигналов на прямом и инверсном выходах наблюдаются одинаковые состояния сигналов. В этом случае нарушается логика работы триггера. Такое состояние триггера называется запрещённым и соответствующая комбинация входных сигналов запрещена. При построении временных диаграмм, если поведение триггера анализируется по его условному обозначению, запрещённое состояние триггера можно не изображать или

выделять каким-либо способом. Если схема триггера представлена на логических элементах, то временные диаграммы могут быть построены для выходных сигналов всех логических элементов и запрещённое состояние триггера может быть выявлено в этом случае по совпадению в течении длительного времени состояний сигналов на прямом и инверсном выходах.

Наиболее распространённые типы триггеров:

Триггер с двумя установочными входами (R - S триггер), изменяющий своё состояние только при воздействии управляющего сигнала на определённый вход (R-или S вход), причём повторное воздействие сигнала на тот же вход Триггер не изменяет его состояния;

Триггер задержки (D-триггер), состояние которого и соответствующий ему выходной сигнал повторяют входной сигнал.

Триггер со счётным входом (Т-триггер), который изменяет своё состояние на противоположное с каждым входным сигналом;

Универсальный триггер (J - K-триггер), обладающий свойствами T-триггера и R - S-триггера;

Кроме триггеров этих типов, применяют комбинированные триггеры, представляющие собой универсальные многофункциональные устройства с большим числом входов.

#### 3. Асинхронный RS-триггер

Асинхронный RS-триггер является базовым при создании более сложных триггеров. В простейшем случае асинхронный RS-триггер имеет два входа: S (Set) - вход установки триггера в единичное состояние, R (Reset) - вход установки триггера в нулевое состояние. Активный сигнал по входу S в момент появления заставляет триггер перейти в единичное состояние. Активный сигнал по входу R в момент появления заставляет триггер перейти в нулевое состояние.

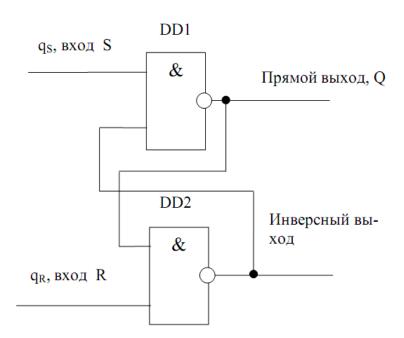

В простейшем случае подобный триггер строится на двух элементах 2И-НЕ. Принципиальная схема триггера представлена на рисунке 1.

Рисунок 1. Функциональная схема RS-триггера

Проанализируем работу этой схемы с целью определения активного сигнала.

Считаем выход элемента DD1 прямым. По заданному положению прямого выхода определим положения входов установки триггера в ноль (R) и в единицу (S). Если предположить, что единица на верхнем входе, то состояние выходного сигнала DD1 будет зависеть от сигнала с выхода DD2. То есть единица на этом входе не заставляет схему непременно менять своё состояние. Это пассивный уровень сигнала на верхнем входе. Если на верхнем входе логический ноль, то независимо от сигнала с DD2 на выходе DD1 спустя время задержки одного элемента tзд появится единица, если её до прихода нуля на верхний вход не было. Сформированная единица, поступая на вход DD2 при наличии на нижнем входе DD2 единицы приведёт к появлению нуля на выходе DD2 спустя время задержки tзд. То есть через время 2tзд состояние сигнала на верхнем входе может быть изменено на противоположное. Триггер к этому моменту перешёл в новое, единичное состояние.

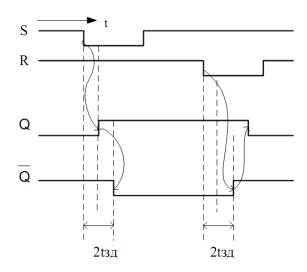

Таким образом, активным сигналом на верхнем входе является 0, этот вход является входом S, поскольку приводит к появлению 1 на выходе Q. Поскольку схема симметрична, можно предположить, что нижний вход является входом сброса триггера в ноль R, причём активным сигналом и для этого входа является ноль. Сигналы на этих входах можно обозначить символами qS, qR. Но в данной работе часто будем обозначать сигналы на временных диаграммах идентификаторами входов, то есть в данном случае буквами S и R. Временные диаграммы работы триггера с учётом задержки сигнала в элементах предложены на рисунке 2.

Рисунок 2. – Временные диаграммы работы RS-триггера с учётом задержки элементов

Если предположить, что на оба входа одновременно подаются активные сигналы, то есть нули, то на обоих выходах формируются одновременно единицы. Триггер оказывается в запрещённом состоянии, которое поддерживается активными сигналами на входах. Если одновременно изменить состояние входных сигналов на пассивное, то в триггере может наблюдаться паразитная генерация с периодом 2tзд, которая прекратится в непредсказуемый момент времени, триггер перейдёт в определённое, но непредсказуемое состояние.

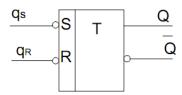

Если триггер реализован в составе микросхемы или необходимо изобразить его на функциональной схеме без показа внутреннего состава, то условное обозначение RS-триггера должно учитывать, что активными сигналами по входам являются нулевые уровни. Следовательно, на входах необходимо изобразить символы инверсии, как показано на рисунке 3.

Рисунок 3. - Условное обозначение асинхронного RS-триггера на электрических схемах

Поведение триггера можно определить сокращённой таблицей переходов (таблица 1), в которой сигналы на входах R и S определены для момента времени t, а состояние триггера определяется для следующего момента времени, который определяют как t+1.

Таблица 1

| qs(t) | qR(t | Q(t+1) | Примечание |

|-------|------|--------|------------|

| 0     | 0    | -      | запрещено  |

| 0     | 1    | 1      | единица    |

| 1     | 0    | 0      | нуль       |

| 1     | 1    | Q(t)   | хранение   |

#### 4. Синхронный одноступенчатый D-триггер.

По сигналу синхронизации на своём прямом выходе D-триггер повторяет состояние сигнала на входе D (Delay).

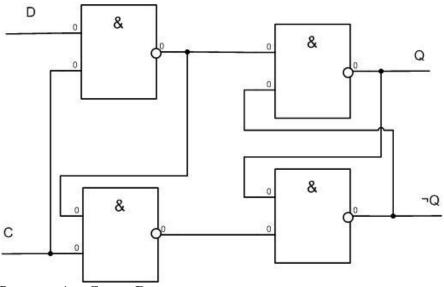

Возможное схемное решение D-триггера предложено на рисунке 4. При C=0 триггер хранит информацию, поскольку на выходах D1, D2 присутствуют единицы, что соответствует пассивным сигналам асинхронного триггера D3, D4. При C=1 в триггер записывается состояние сигнала D. Если D=0, то на выходе D1формируется единица, а на выходе D2 формируется ноль, что приводит к записи в триггер нуля.

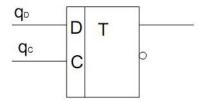

Условное обозначение D-триггера приведено на рисунке 5.

Рисунок 4. – Схема D-триггера с потенциальным управлением

Рисунок 5 Условное обозначение D-триггера

Поведение триггера описывается таблицей переходов (таблица 2).

Таблица 1. Таблица переходов D-триггера

| _ |   |        | - 1                                |                                 |  |

|---|---|--------|------------------------------------|---------------------------------|--|

| С | D | Q(t-1) | Q(t)                               | Пояснения                       |  |

| 0 | x | 0      | 0<br>Режим хранения информаци<br>1 |                                 |  |

| 0 | х | 1      |                                    |                                 |  |

| 1 | 0 | х      | 0                                  | )<br>—— Режим записи информации |  |

| 1 | 1 | х      | 1                                  |                                 |  |

Для D-триггера нет запрещённой комбинации сигналов на входах D и C.

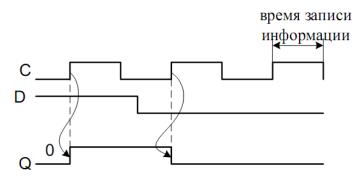

Поведение D-триггера изображено на временных диаграммах, изображённых на рисунке 6.

Рисунок 6. – Временные диаграммы работы D-триггера

При активном синхросигнале нежелательно менять состояние сигнала на информационном входе D. В момент окончания действия активного синхросигнала происходит переход триггера из режима записи в режим хранения принятой информации. Как бы триггер защёлкивается в новом состоянии. Поэтому подобные триггеры иногда называют триггерами-защёлками.

Обратите внимание на тот факт, что при активном синхросигнале изменение состояния сигнала на входе D повторяется на выходе. То есть триггер превращается в повторитель входного сигнала. Этим фактом иногда пользуются для повышения, например, нагрузочной способности схемы.

#### 5. Задание на лабораторную работу.

- 1) Собрать RS-триггер по схеме, изображенной на рисунке 2.1. Проверить работу схемы на осциллографе, зарисовать диаграммы, составить таблицы переходов.

- 2) Собрать D-триггер по схеме, изображенной на рисунке 2.4. Проверить работу схемы на осциллографе, зарисовать диаграммы, составить таблицы переходов.

- 3) По результатам работы сформировать отчёт.

### 6. Содержание отчёта

Отчёт должен содержать:

- Схему собираемого устройства;

- Временные диаграммы работы устройства;

- Таблицы переходов триггеров.

#### 7. Контрольные вопросы:

- Что называется триггером?

- Типы триггеров

- Нарисуйте временные диаграммы работы синхронного и асинхронного RSтриггеров.

- Какая комбинация на входах RS-триггера называется запрещенной и почему?

- Что такое время подготовки и время выдержки D-триггера и почему они имеют такие значения?

- В чем отличие JK-триггера от RS-триггера?

- Принцип работы синхронного D-триггера.

- Почему возникает необходимость в построении двухступенчатых триггерных устройств?