# Схемотехника (углубленный курс)

Лекция №4

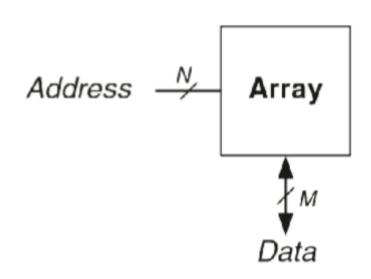

#### Матрицы памяти

#### ПЗУ

```

module imem (

input logic [5:0] a,

output logic [31:0] rd

);

logic [31:0] RAM[63:0];

initial

$readmemh("memfile.dat", RAM);

assign rd = RAM[a];

endmodule

```

#### О3У

```

module dmem (

input logic clk, we,

input logic [31:0] a, wd,

output logic [31:0] rd

);

logic [31:0] RAM[63:0];

assign rd = RAM[a[31:2]];

always ff @(posedge clk)

if (we) RAM[a[31:2]] <= wd;

endmodule

```

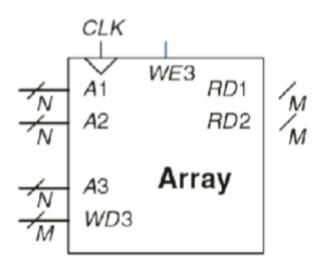

#### Файл регистров

```

|module regfile(

input logic clk,

input logic we3,

input logic [4:0] ra1, ra2, wa3,

input logic [31:0] wd3,

output logic [31:0] rd1, rd2

);

logic [31:0] rf[31:0];

always ff @(posedge clk)

if (we3) rf[wa3] <= wd3;</pre>

assign rd1 = (ra1 != 0) ? rf[ra1] : 0;

assign rd2 = (ra2 != 0) ? rf[ra2] : 0;

endmodule

```

## Регистры архитектуры MIPS

| Название  | Номер | Назначение                                   |

|-----------|-------|----------------------------------------------|

| \$0       | 0     | Константный нуль                             |

| \$at      | 1     | Временный регистр для нужд ассемблера        |

| \$v0-\$v1 | 2–3   | Возвращаемые функциями значения              |

| \$a0-\$a3 | 4–7   | Аргументы функций                            |

| \$t0-\$t7 | 8–15  | Временные переменные                         |

| \$s0-\$s7 | 16–23 | Сохраняемые переменные                       |

| \$t8-\$t9 | 24–25 | Временные переменные                         |

| \$k0-\$k1 | 26–27 | Временные переменные операционной системы    |

| \$gp      | 28    | Глобальный указатель (англ.: global pointer) |

| \$sp      | 29    | Указатель стека (англ.: stack pointer)       |

| \$fp      | 30    | Указатель кадра стека (англ.: frame pointer) |

| \$ra      | 31    | Регистр адреса возврата из функции           |

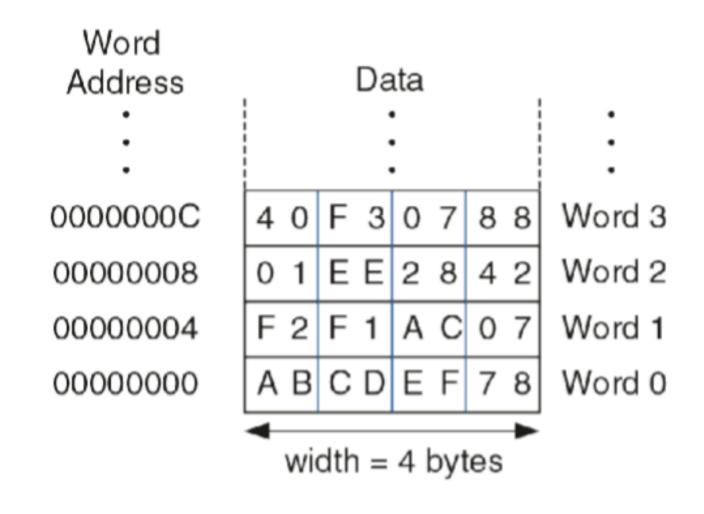

## Память с побайтовой адресацией

## Доступ к памяти

```

lw $s0, 0($0)  # read data word 0 (0xABCDEF78) into $s0

lw $s1, 8($0)  # read data word 2 (0x01EE2842) into $s1

lw $s2, 0xC($0)  # read data word 3 (0x40F30788) into $s2

sw $s3, 4($0)  # write $s3 to data word 1

sw $s4, 0x20($0)  # write $s4 to data word 8

sw $s5, 400($0)  # write $s5 to data word 100

```

#### Непосредственные операнды

#### Код на языке высокого уровня

```

a = a + 4;

b = a - 12;

```

#### Код на языке ассемблера MIPS

```

# $s0 = a, $s1 = b

addi $s0, $s0, 4 # a = a + 4

addi $s1, $s0, -12 # b = a - 12

```

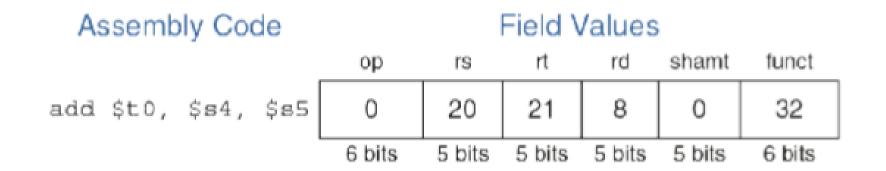

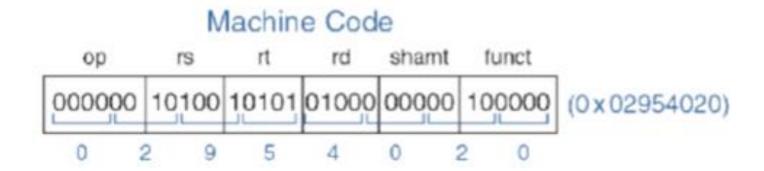

# Формат команды типа R

| ор     | rs     | rt     | rd     | shamt  | funct  |

|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

## Примеры команд типа R

| 100000 (32) add rd, rs, rt       | сложение со знаком,<br>арифметическое<br>переполнение вызвает<br>исключение (add)       | [rd] = [rs] + [rt] |

|----------------------------------|-----------------------------------------------------------------------------------------|--------------------|

| 100010 (34) sub rd, rs, rt       | Вычитание со знаком,<br>арифметическое<br>переполнение вызвает<br>исключение (subtract) | [rd] = [rs] - [rt] |

| 100100 (36) and rd, rs, rt       | побитовое логическое «И»<br>(and)                                                       | [rd] = [rs] & [rt] |

| <b>100101 (37)</b> or rd, rs, rt | побитовое логическое<br>«ИЛИ» (or)                                                      | [rd] = [rs]   [rt] |

# Битовый сдвиг

| Funct      | Имя               | Описание                                                                       | Операция                            |

|------------|-------------------|--------------------------------------------------------------------------------|-------------------------------------|

| 000000 (0) | sll rd, rt, shamt | логический сдвиг влево<br>(shift left logical)                                 | [rd] = [rt] << shamt                |

| 000010 (2) | srl rd, rt, shamt | логический сдвиг вправо<br>(shift right logical)                               | [rd] = [rt] >> shamt                |

| 000011 (3) | sra rd, rt, shamt | арифметический сдвиг<br>вправо (shift right arithmetic)                        | [rd] = [rt] >>> shamt               |

| 000100 (4) | sllv rd, rt, rs   | логический переменный<br>сдвиг влево (shift left logical<br>variable)          | [rd] = [rt] << [rs] <sub>4:0</sub>  |

| 000110 (6) | srlv rd, rt, rs   | логический переменный<br>сдвиг вправо (shift right<br>logical variable)        | [rd] = [rt] >> [rs] <sub>4:0</sub>  |

| 000111 (7) | srav rd, rt, rs   | арифметический<br>переменный сдвиг вправо<br>(shift right arithmetic variable) | [rd] = [rt] >>> [rs] <sub>4:0</sub> |

#### Пример трансляции команды типа R

## Формат команды типа I

| op     | rs     | rt     | imm     |

|--------|--------|--------|---------|

| 6 bits | 5 bits | 5 bits | 16 bits |

#### Примеры опкодов команд типа І

| Opcode      | Имя              | Описание                                                                                                                        | Операция                    |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 001000 (8)  | addi rt, rs, imm | сложение с<br>непосредственным<br>операндом со знаком,<br>арифметическое<br>переполнение вызывает<br>исключение (add immediate) | [rt] = [rs] + SignImm       |

| 001101 (13) | ori rt, rs, imm  | побитовое логическое<br>«ИЛИ» с непосредственным<br>операндом, расширенным<br>влево нулями (or immediate)                       |                             |

| 100011 (35) | lw rt, imm(rs)   | загрузка слова (load word)                                                                                                      | <pre>[rt] = [Address]</pre> |

| 101011 (43) | sw rt, imm(rs)   | сохранение слова<br>(store word)                                                                                                | [Address] = [rt]            |

|      |       | -         | ор     | rs     | rt     | imm                 |                |

|------|-------|-----------|--------|--------|--------|---------------------|----------------|

| addi | \$s0, | \$s1, 5   | 8      | 17     | 16     | 5                   |                |

| addi | \$t0, | \$s3, -12 | 8      | 19     | 8      | -12                 |                |

| lw   | \$t2, | 32(\$0)   | 35     | 0      | 10     | 32                  |                |

| sw   | \$s1, | 4(\$t1)   | 43     | 9      | 17     | 4                   |                |

|      |       |           | 6 bits | 5 bits | 5 bits | 16 bits             |                |

|      |       |           | ор     | rs     | rt     | imm                 |                |

|      |       |           | 001000 | 10001  | 10000  | 0000 0000 0000 0101 | (0x22300005)   |

|      |       |           | 001000 | 10011  | 01000  | 1111 1111 1111 0100 | (0x2268FFF4)   |

|      |       |           | 100011 | 00000  | 01010  | 0000 0000 0010 0000 | (0x8C0A0020)   |

|      |       |           | 101011 | 01001  | 10001  | 0000 0000 0000 0100 | (0 x AD310004) |

|      |       |           | 6 bits | 5 bits | 5 bits | 16 bits             |                |

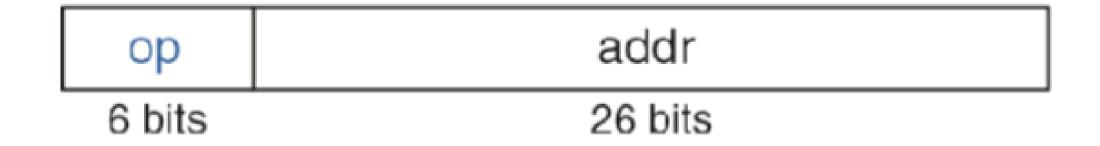

## Формат команды типа Ј

## Примеры опкодов команд переходов

| 000001 (1)<br>(rt = 0/1) | bltz rs, label /<br>bgez rs, label | ветвление, если меньше<br>нуля (branch less than zero) и<br>ветвление, если больше или<br>равно нулю (branch greater<br>than or equal to zero) | if ([rs] < 0) PC = /BTA/ if ([rs] > 0) PC = BTA |

|--------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 000010 (2)               | j label                            | безусловный переход (jump                                                                                                                      | ) PC = JTA                                      |

| 000011 (3)               | jal label                          | безусловный переход с<br>возвратом (jump and link)                                                                                             | pc = pc + 4, pc = JTA                           |

| 000100 (4)               | beq rs, rt, label                  | ветвление, если равно<br>(branch if equal)                                                                                                     | if ([rs] == [rt])<br>PC = BTA                   |

#### Режимы адресации

- Регистровая адресация (инструкции типа R)

- Непосредственная адресация (16-битные константы некоторых инструкций типа I)

- Базовая адресация (база из регистра плюс 16-битное смещение)

- Адресация относительно счетчика команд (ВТА)

- Псевдопрямая адресация (JTA)

#### Вычисление адресов переходов

```

BTA: целевой адрес ветвления

= PC + 4 + (SignImm << 2)

JTA: адрес перехода

= {(PC + 4)[31:28], addr, 2'b0}

```

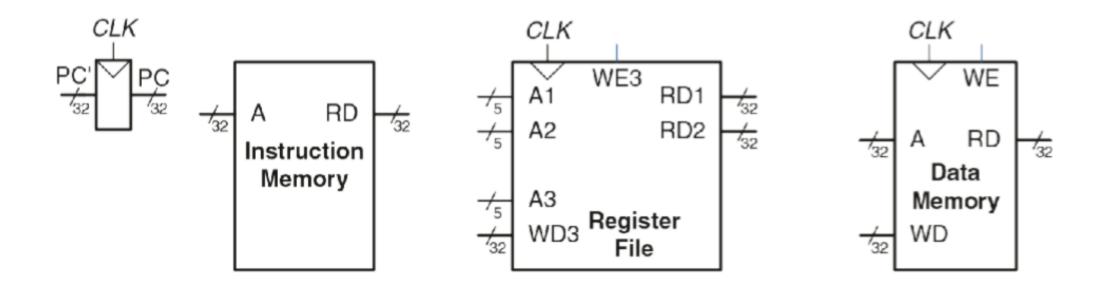

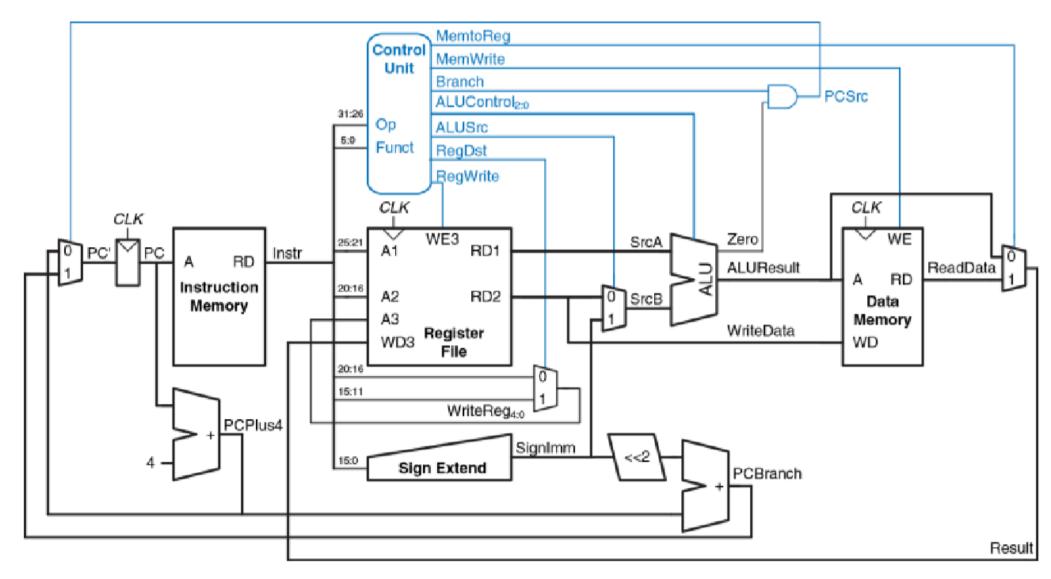

#### Элементы, хранящие состояние процессора

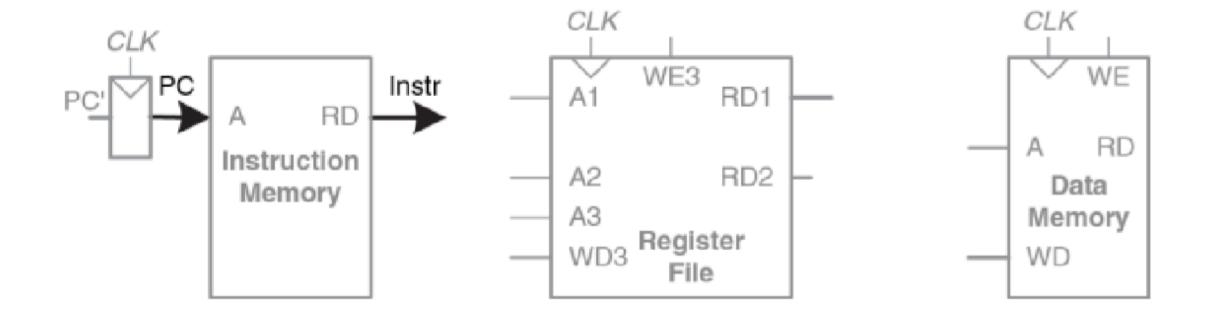

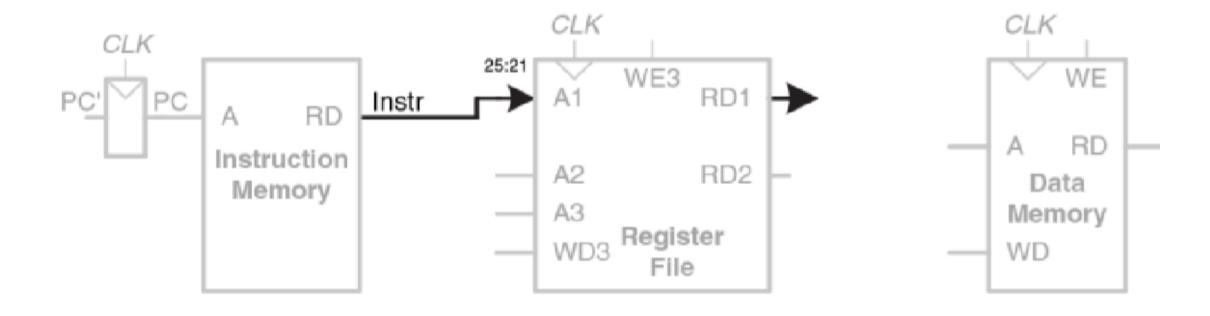

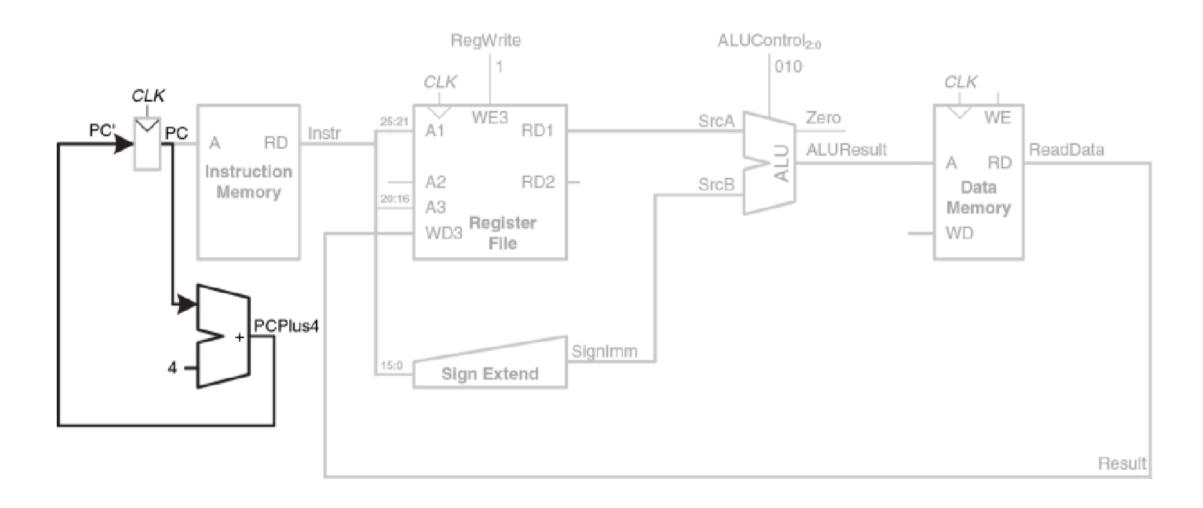

## Выборка команды из памяти

#### Чтение операнда из регистрового файла

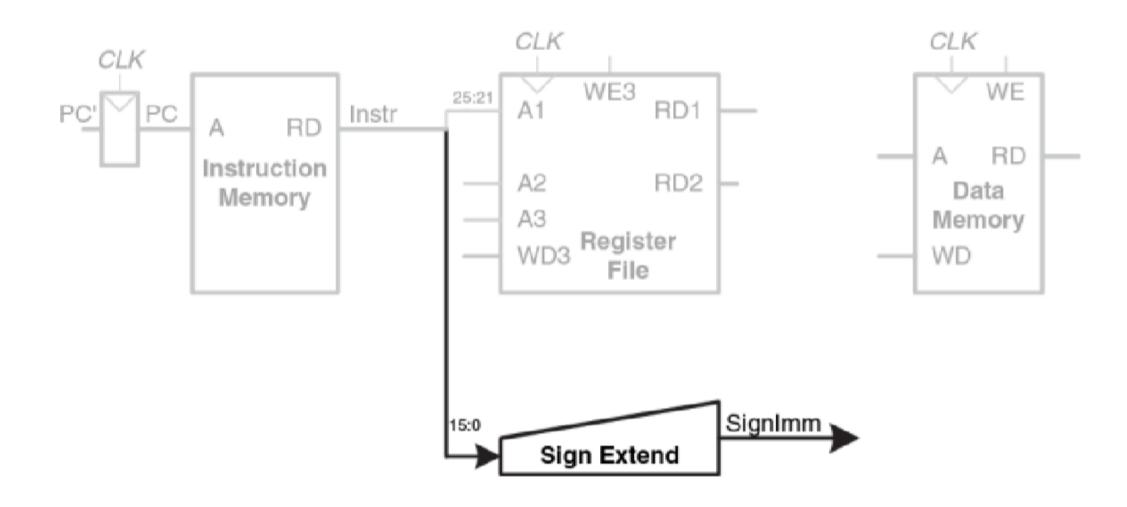

#### Знаковое расширение непосредственного операнда

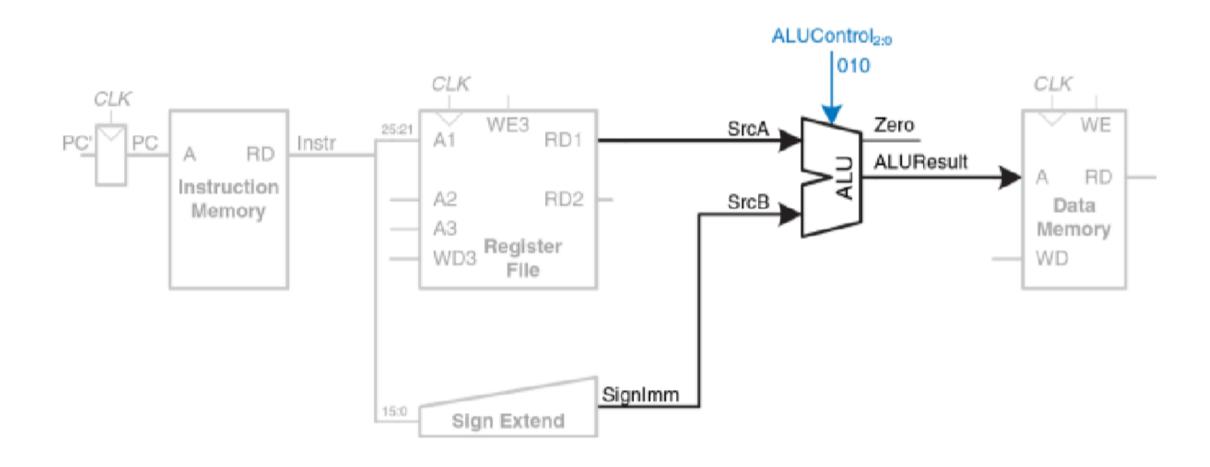

#### Вычисление адреса данных в памяти

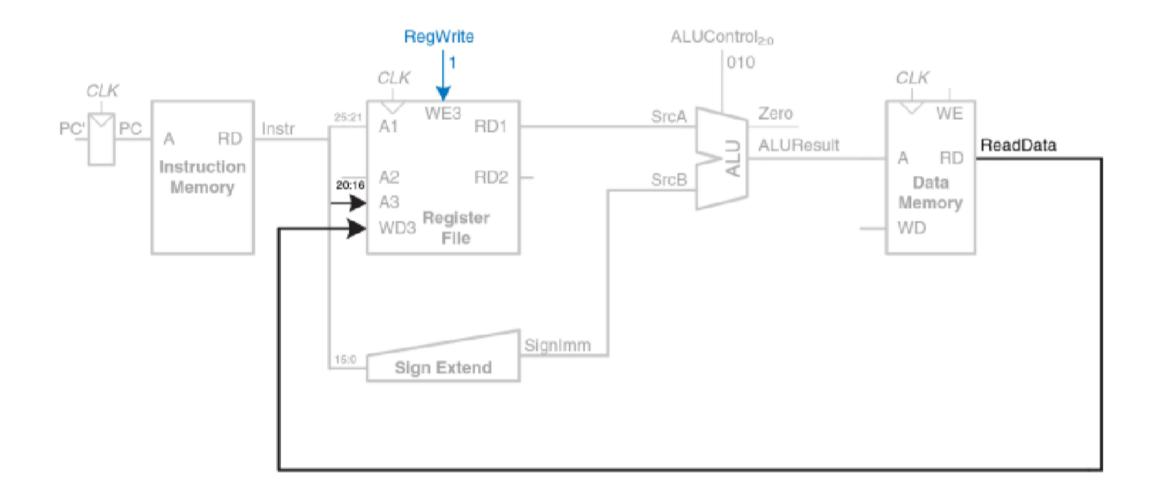

## Запись в регистровый файл

#### Определение адреса следующей команды

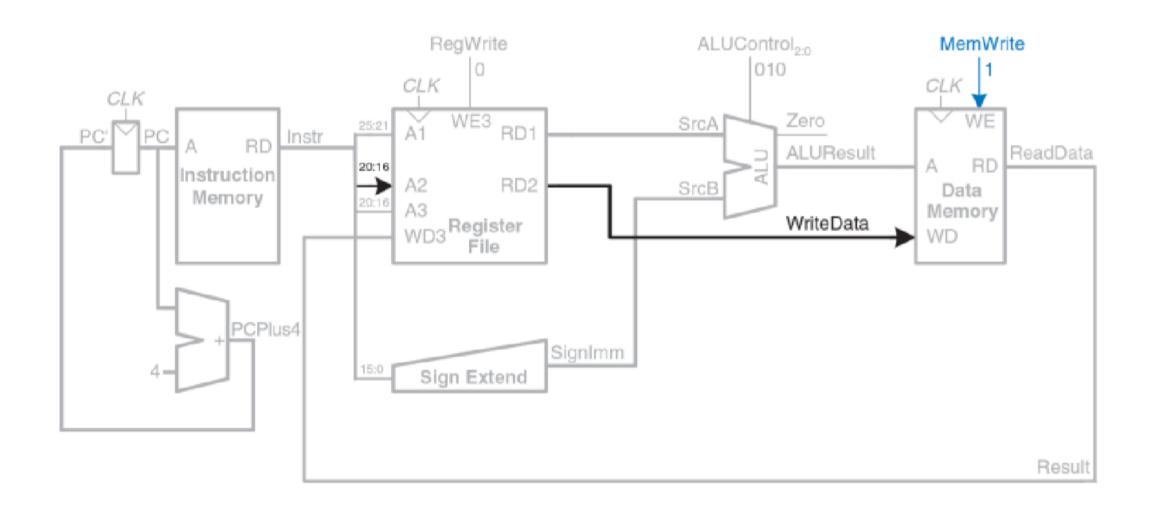

#### Запись командой **sw** данных в память

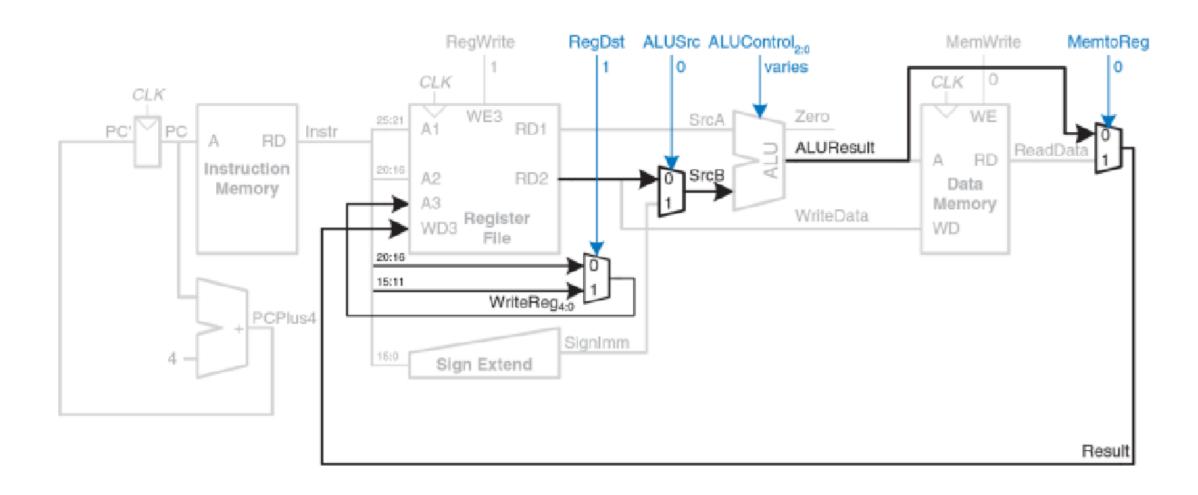

#### Поддержка команд типа **R**

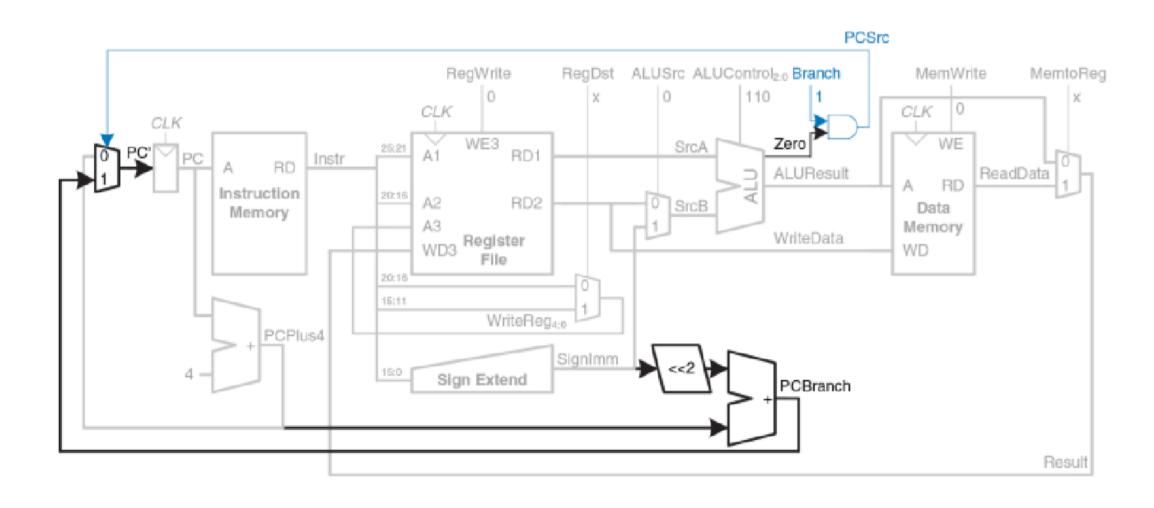

#### Поддержка команды **beq**

## Однотактный процессор

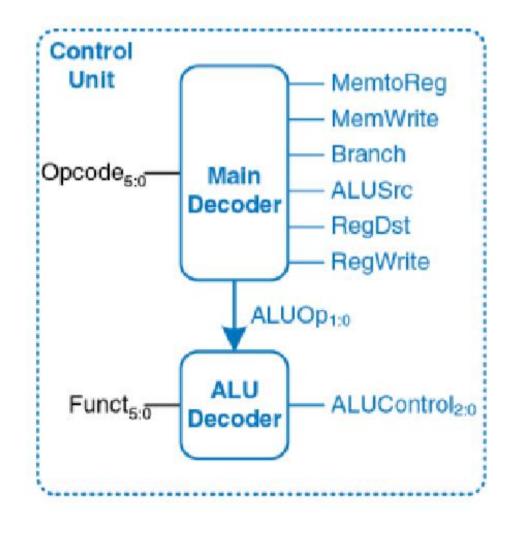

# Устройство управления

| Сложение                 |

|--------------------------|

| Вычитание                |

| Определяется полем funct |

| Не используется          |

|                          |

| ALUOp | funct                        | ALUControl                    |

|-------|------------------------------|-------------------------------|

| 00    | X                            | 010 (сложение)                |

| X1    | Χ                            | 110 (вычитание)               |

| 1X    | <b>100000 (</b> add <b>)</b> | 010 (сложение)                |

| 1X    | 100010 (sub)                 | 110 (вычитание)               |

| 1X    | <b>100100 (</b> and <b>)</b> | 000 (логическое «И»)          |

| 1X    | 100101 (or)                  | 001 (логическое «ИЛИ»)        |

| 1X    | <b>101010 (</b> slt <b>)</b> | 111 (установить, если меньше) |

| Команда           | Opcode | RegWrite | RegDst | ALUSrc | Branch | MemWrite | MemtoReg | J ALUOp |

|-------------------|--------|----------|--------|--------|--------|----------|----------|---------|

| Команды<br>типа R | 000000 | 1        | 1      | 0      | 0      | 0        | 0        | 10      |

| lw                | 100011 | 1        | 0      | 1      | 0      | 0        | 1        | 00      |

| SW                | 101011 | 0        | Χ      | 1      | 0      | 1        | Χ        | 00      |

| beq               | 000100 | 0        | Χ      | 0      | 1      | 0        | Х        | 01      |